Logické obvody (X36LOB)

Semestrální práce

Vypracoval: Marek Handl

Studijní skupina: 226

Kontakt: mean.marine@seznam.cz

Datum: prosinec 2005

Obsah:

- Zadání

- Minimalizace vnitřních stavů

- Binární kódování

- Zakódování vnitřních stavů

- Karnaughovy mapy

- Výrazy pro budící proměnné klopných obvodů

- Schéma

- Maximální frekvence

- Výstup simulace

- Výstup implementace

- Kódování Grayovym kódem

- Zakódování vnitřních stavů

- Karnaughovy mapy

- Výrazy pro budící proměnné klopných obvodů

- Schéma

- Maximální frekvence

- Výstup simulace

- Výstup implementace

- Závěr

1. Zadání

-

Pomocí synchronního sekvenčního obvodu realizujte konečný automat se dvěma

vstupy a, b a jedním výstupem z, zadaný následující tabulkou přechodů

a tabulkou výstupů. Minimalizujte počet vnitřních stavů a použijte vhodné zakódování

vnitřních stavů. Výsledné schéma implementujte v Xilinx ISE a nahrajte do přípravku XCRP.

Vstupy ovládejte přepínači, výstup a všechny vnitřní proměnné vyveďte

na LED diody. Pro hodinový signál a signál reset (použijte klopné obvody s asynchronním nulováním)

použijte tlačítka. Správnost návrhu ověřte na přípravku podle tabulky přechodů a výstupů.

\ba| tabulka přechodů tabulka výstupů

Qi\ | 00 01 10 00 01 10

-------------------- --------------

Q0| Q13 Q2 Q2 1 0 1

Q1| Q11 Q4 Q5 1 1 0

Q2| Q11 Q13 Q13 0 1 1

Q3| Q0 Q0 Q11 0 1 1

Q4| Q0 Q10 Q11 0 1 1

Q5| Q3 Q9 Q9 0 1 0

Q6| Q3 Q1 Q12 0 1 0

Q7| Q6 Q1 Q1 0 1 1

Q8| Q4 Q13 Q9 0 1 0

Q9| Q11 Q3 Q5 1 1 0

Q10| Q13 Q7 Q7 1 0 1

Q11| Q4 Q9 Q12 0 1 0

Q12| Q4 Q8 Q11 0 1 1

Q13| Q6 Q4 Q8 1 1 0

Použijte klopné obvody typu T(FTC) .

- Použijte buď NAND nebo NOR hradla.

- Vnější vstupy máte k dispozici pouze v přímé formě.

- Zpoždění obvodů pro hradla i pro klopné obvody naleznete v přednáškách.

-

Stanovte maximální možnou hodinovou frekvenci za předpokladů:

Vstupní stavy obvodu se mění pouze v intervalu < T , T + 3 ns >,

kde T jsou okamžiky příchodu záporné hrany hodinových pulzů.

Správný výstupní stav musí trvat po dobu nejméně 3 ns.

2. Minimalizace počtu stavů:

Minimalizaci provedu pomocí implikační tabulky. Z důvodu přehlednosti vynechávám písmeno Q.

V prvním kroku zakřížkuji všechny dvojice stavů, které nemohou být totožné, protože

se liší výstupem. U dvojic stavů, které jsou z hlediska výstupu totožné nechám zatím políčko prázdné.

| 0 | X | | | | | | | | | | | | | |

|---|

| 1 | X | X | | | | | | | | | | | | |

|---|

| 2 | X | X | X | | | | | | | | | | | |

|---|

| 3 | X | X | | X | | | | | | | | | | |

|---|

| 4 | X | X | | | X | | | | | | | | | |

|---|

| 5 | X | X | X | X | X | X | | | | | | | | |

|---|

| 6 | X | X | X | X | X | | X | | | | | | | |

|---|

| 7 | X | X | | | | X | X | X | | | | | | |

|---|

| 8 | X | X | X | X | X | | | X | X | | | | | |

|---|

| 9 | X | | X | X | X | X | X | X | X | X | | | | |

|---|

| 10 | | X | X | X | X | X | X | X | X | X | X | | | |

|---|

| 11 | X | X | X | X | X | | | X | | X | X | X | | |

|---|

| 12 | X | X | | | | X | X | | X | X | X | X | X | |

|---|

| 13 | X | | X | X | X | X | X | X | X | | X | X | X | X |

|---|

| | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 |

|---|

Do prázdných políček doplňuji podmínky, kdy by se odpovídající stavy rovnaly, pokud je podmínka na první pohled nesplnitelná

vpisuji X.

| 0 | X | | | | | | | | | | | | | |

|---|

| 1 | X | X | | | | | | | | | | | | |

|---|

| 2 | X | X | X | | | | | | | | | | | |

|---|

| 3 | X | X | X | X | | | | | | | | | | |

|---|

| 4 | X | X | X | 0=10 | X | | | | | | | | | |

|---|

| 5 | X | X | X | X | X | X | | | | | | | | |

|---|

| 6 | X | X | X | X | X | X | X | | | | | | | |

|---|

| 7 | X | X | 6=11

1=13 | X | X | X | X | X | | | | | | |

|---|

| 8 | X | X | X | X | X | 3=4

9=13 | X | X | X | | | | | |

|---|

| 9 | X | 3=4 | X | X | X | X | X | X | X | X | | | | |

|---|

| 10 | 2=7 | X | X | X | X | X | X | X | X | X | X | | | |

|---|

| 11 | X | X | X | X | X | X | 3=4

1=9 | X | X | X | X | X | | |

|---|

| 12 | X | X | X | X | X | X | X | X | X | X | X | X | X | |

|---|

| 13 | X | 6=11

5=8 | X | X | X | X | X | X | X | 6=11

3=4

5=8 | X | X | X | X |

|---|

| | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 |

|---|

Všechny podmínky jsou splnitelné, takže dostáváme rovnosti stavů:

- Q0 = Q10

- Q1 = Q9 = Q13

- Q2 = Q7

- Q3 = Q4

- Q5 = Q8

- Q6 = Q11

Zminimalizovaná tabulka přechodů a výstupů:

\ba| tabulka přechodů tabulka výstupů

Qi\ | 00 01 10 00 01 10

-------------------- --------------

Q0| Q1 Q2 Q2 1 0 1

Q1| Q6 Q3 Q5 1 1 0

Q2| Q6 Q1 Q1 0 1 1

Q3| Q0 Q0 Q6 0 1 1

Q5| Q3 Q1 Q1 0 1 0

Q6| Q3 Q1 Q12 0 1 0

Q12| Q3 Q5 Q6 0 1 1

Pro zakódování vnitřních stavů zkusím binární kódování a grayův kód. Provedu všechny potřebné výpočty a porovnám výsledky.

Metodu Dollota and McCluskeyho nepoužiji, protože je určena pro klopné obvody typu D.

3. Binární kódování

a) Zakodovaná tabulka přechodů a výstupů:

| 00 01 10 | 00 01 10

cde | cde cde cde | y y y

--------------------------------------------

Q0 000 | 001 010 010 | 1 0 1

Q1 001 | 101 011 100 | 1 1 0

Q2 010 | 101 001 001 | 0 1 1

Q3 011 | 000 000 101 | 0 1 1

Q5 100 | 011 001 001 | 0 1 0

Q6 101 | 011 001 110 | 0 1 0

Q12 110 | 011 100 101 | 0 1 1

b) Karnaughovy mapy s vyznačenými "tlustými znaky" pro vstupy klopných obvodů a mapa pro výstupní proměnnou:

| c: |

|

d: |

|

e: |

|

y: |

|

|

|

|

d |

|

|

|

d |

|

|

|

d |

|

|

|

d |

|

|

|

e |

|

|

|

e |

|

|

|

e |

|

|

|

e |

|

|

|

|

|

|

0 |

1 |

0 |

1 |

|

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

|

|

|

0 |

0 |

X |

0 |

|

|

1 |

1 |

X |

1 |

|

|

1 |

1 |

X |

1 |

|

|

0 |

0 |

X |

0 |

|

|

|

|

0 |

1 |

X |

1 |

|

|

|

0 |

1 |

X |

0 |

|

|

|

1 |

0 |

X |

1 |

|

|

|

0 |

0 |

X |

1 |

|

|

|

|

0 |

1 |

1 |

0 |

|

|

|

1 |

0 |

0 |

0 |

|

|

|

0 |

0 |

1 |

1 |

|

|

|

1 |

0 |

1 |

1 |

|

|

|

|

|

X |

X |

X |

X |

|

|

|

|

X |

X |

X |

X |

|

|

|

|

X |

X |

X |

X |

|

|

|

|

X |

X |

X |

X |

|

|

|

|

|

X |

X |

X |

X |

|

|

|

|

X |

X |

X |

X |

|

|

|

|

X |

X |

X |

X |

|

|

|

|

X |

X |

X |

X |

|

|

b |

|

0 |

0 |

X |

1 |

|

b |

|

0 |

0 |

X |

0 |

|

b |

|

1 |

1 |

X |

0 |

|

b |

|

1 |

1 |

X |

1 |

|

|

|

c |

0 |

0 |

0 |

0 |

|

|

c |

1 |

1 |

0 |

0 |

|

|

c |

0 |

1 |

0 |

1 |

|

|

c |

0 |

1 |

1 |

1 |

|

| a |

|

a |

|

a |

|

a |

|

c) Výrazy pro budící proměnné klopných obvodů (typ T) a vnější výstup v MNDF:

- c = a·c·e + b·c·e + c·d·e + a·b·d·e + a·b·d·e

- d = a·c + a·d + b·d + c·d + b·c·e + b·c·e + a·b·c·d

- e = b·c·d + a·d·e + b·d·e + c·d·e + a·b·d·e

- y = a·c + a·d + a·e + b·d + b·c·e + a·b·c·d

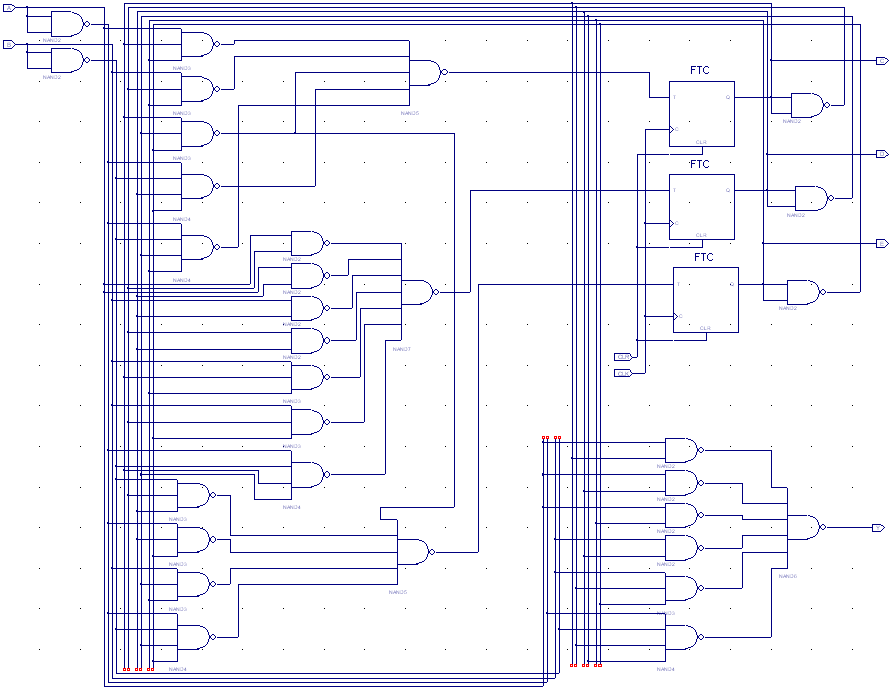

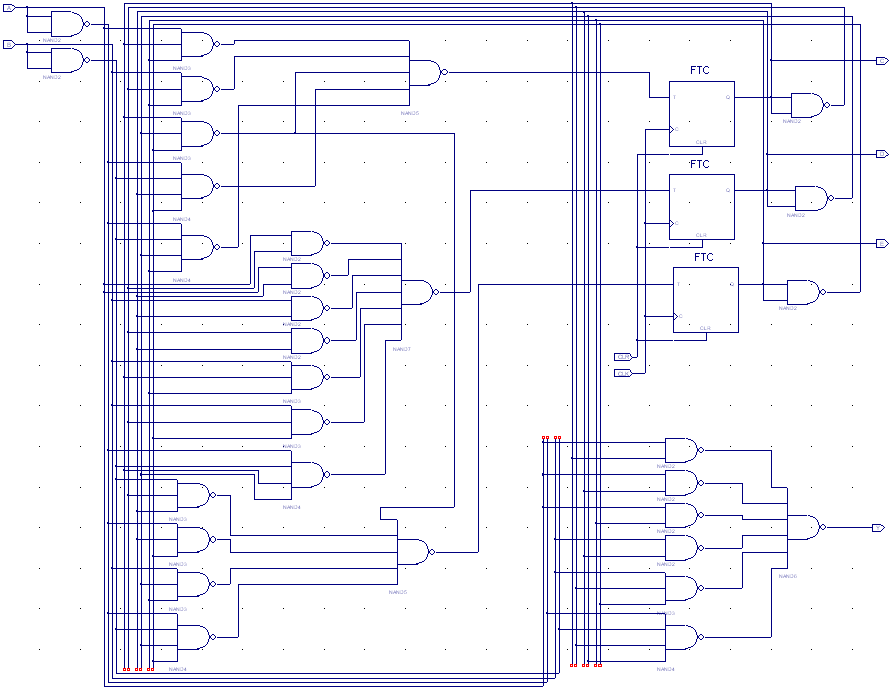

d) Schéma zapojení:

Rozhodl jsem se pro použití hradel NAND.

Zdrojový soubor se schématem:

schema_bin.sch

e) Výpočet maximální frekvence:

Zpoždění v ns:

| NestabilniVstup |

3 |

| StabilniVystup |

3 |

| ClockToQ |

3 |

| Setup |

1 |

| NAND2 |

1.4 |

| NAND4 |

2.2 |

| NAND6 |

3 |

| NAND7 |

3.4 |

Hledám kritickou cestu:

- Ze vstupu na vstup klopného obvodu

NestabilniVstup + NAND2 + NAND4 + NAND7 + Setup = 3 + 1.4 + 2.2 + 3.4 + 1 = 11 ns

- Z výstupu klopného obvodu na výstup

ClockToQ + NAND2 + NAND4 + NAND6 + StabilniVystup = 3 + 1.4 + 2.2 + 3 + 3 = 12.6 ns

- Ze vstupu na výstup

NestabilniVstup + NAND2 + NAND4 + NAND6 + StabilniVystup = 3 + 1.4 + 2.2 + 3 + 3 = 12.6 ns

- Z výstupu klopného obvodu na vstup klopného obvodu

ClockToQ + NAND2 + NAND4 + NAND7 + Setup = 3 + 1.4 + 2.2 + 3.4 + 1 = 11 ns

Kritická cesta tedy zabere 12,6 ns, z čehož dostáváme maximální možnou frekvenci cca. 79 MHz.

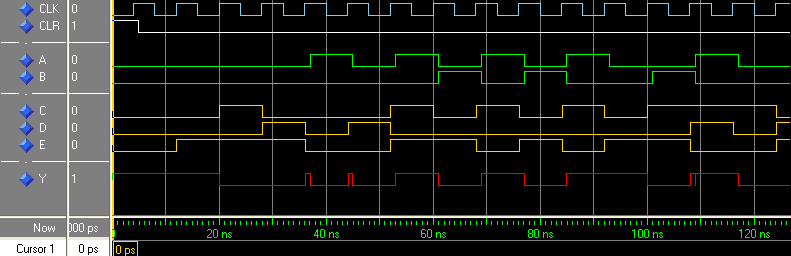

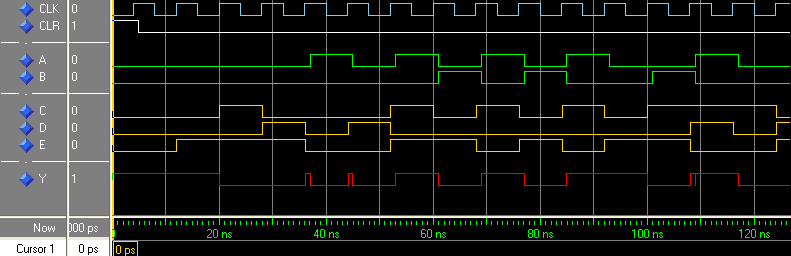

f) Časový diagram získaný ze simulace:

Abych prošel všechny stavy (podle původní nezminimalizované tabulky přechodů) zvolil jsem takovýto průchod.

(Qi =ba=> Qj značí toto: Qi je výchozí stav, poté přijdou na vstup hodnoty a, b a automat přejde do stavu Qj.)

Q0 =00=> Q13 =00=> Q6 =00=> Q3 =00=> Q0 =01=> Q2 =00=> Q11 =00=> Q4 =01=> Q10 =10=> Q7 =01=> Q1 =10=> Q5 =01=> Q9 =00=> Q11 =10=> Q12 =01=> Q8

Což se díky rovnosti některých stavů dá přepsat takto:

Q0 =00=> Q1 =00=> Q6 =00=> Q3 =00=> Q0 =01=> Q2 =00=> Q6 =00=> Q3 =01=> Q0 =10=> Q2 =01=> Q1 =10=> Q5 =01=> Q1 =00=> Q6 =10=> Q12 =01=> Q5

g) Výstup implementace:

Hodnota maximální frekvence je 192,308 MHz, využívá se 7% makrobuněk, 10% Ptermů, 5% registrů, 25% pinů a 4% vstupů funkčních bloků.

Kompletní zpráva o implementaci pro binární kódování je

zde.

4. Grayův kód

a) Zakodovaná tabulka přechodů a výstupů:

| 00 01 10 | 00 01 10

cde | cde cde cde | y y y

--------------------------------------------

Q0 000 | 001 011 011 | 1 0 1

Q1 001 | 111 010 110 | 1 1 0

Q2 011 | 111 001 001 | 0 1 1

Q3 010 | 000 000 111 | 0 1 1

Q5 110 | 010 001 001 | 0 1 0

Q6 111 | 010 001 101 | 0 1 0

Q12 101 | 010 110 111 | 0 1 1

b) Karnaughovy mapy s vyznačenými "tlustými znaky":

| c: |

|

|

|

|

|

|

d: |

|

|

|

|

|

|

e: |

|

|

|

|

|

|

y: |

|

|

|

|

|

|

|

|

d |

|

|

|

d |

|

|

|

d |

|

|

|

d |

|

|

|

e |

|

|

|

e |

|

|

|

e |

|

|

|

e |

|

|

|

|

|

|

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

0 |

|

|

|

X |

0 |

0 |

0 |

|

|

X |

1 |

1 |

1 |

|

|

X |

0 |

0 |

0 |

|

|

X |

0 |

0 |

0 |

|

|

|

|

X |

1 |

1 |

0 |

|

|

|

X |

1 |

0 |

0 |

|

|

|

X |

1 |

1 |

1 |

|

|

|

X |

1 |

0 |

0 |

|

|

|

|

0 |

1 |

0 |

1 |

|

|

|

1 |

1 |

0 |

1 |

|

|

|

1 |

0 |

1 |

1 |

|

|

|

1 |

0 |

1 |

1 |

|

|

|

|

|

X |

X |

X |

X |

|

|

|

|

X |

X |

X |

X |

|

|

|

|

X |

X |

X |

X |

|

|

|

|

X |

X |

X |

X |

|

|

|

|

|

X |

X |

X |

X |

|

|

|

|

X |

X |

X |

X |

|

|

|

|

X |

X |

X |

X |

|

|

|

|

X |

X |

X |

X |

|

|

b |

|

X |

1 |

0 |

0 |

|

b |

|

X |

1 |

0 |

0 |

|

b |

|

X |

0 |

1 |

1 |

|

b |

|

X |

1 |

1 |

1 |

|

|

|

c |

0 |

0 |

0 |

0 |

|

|

c |

1 |

1 |

0 |

0 |

|

|

c |

1 |

0 |

1 |

0 |

|

|

c |

0 |

1 |

1 |

1 |

|

| a |

|

a |

|

a |

|

a |

|

c) Výrazy pro budící proměnné klopných obvodů (typ T) a vnější výstup v MNDF:

- c = c·e + a·b·e + a·c·d + b·d·e + b·c·d·e

- d = a + b·c + b·d + b·e + d·e + b·c·d·e

- e = a·d + b·e + d·e + a·c·e + b·c·d + a·b·c·e

- y = a·e + a·d + b·c·d + b·c·d + b·c·e + a·b·c·d

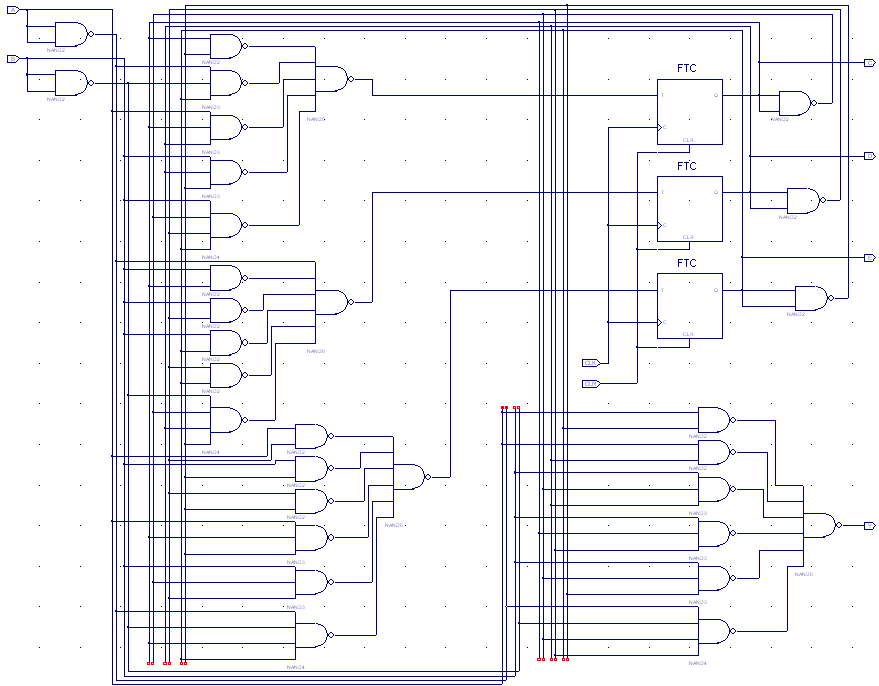

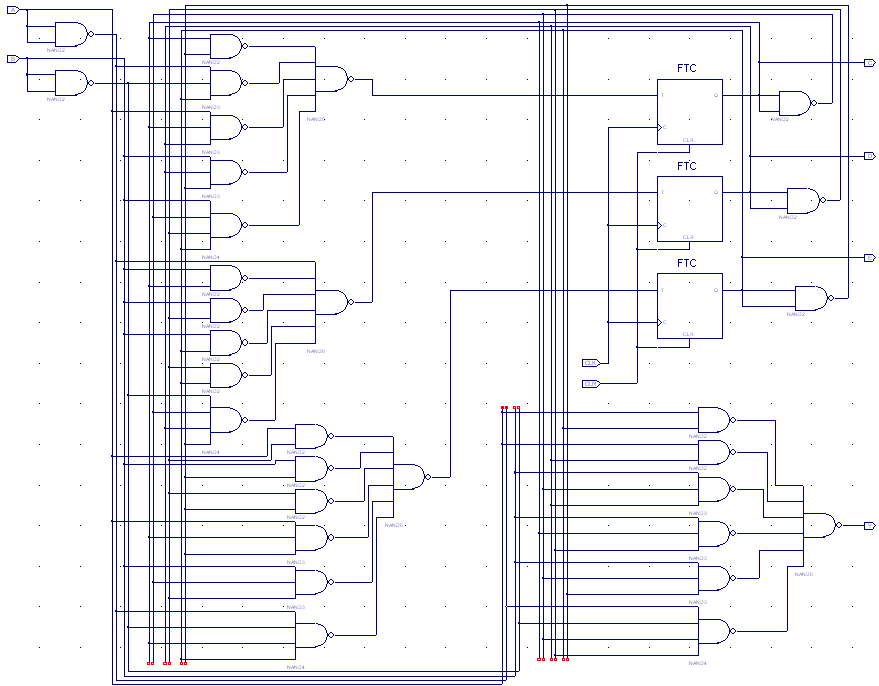

d) Schéma zapojení:

Opět používám hradla NAND.

Zdrojový soubor se schématem:

schema_gray.sch

e) Výpočet maximální frekvence:

Počítám se stejnými hodnotami zpoždění jako u binárního kódování.

Hledám kritickou cestu:

- Ze vstupu na vstup klopného obvodu

NestabilniVstup + NAND2 + NAND4 + NAND6 + Setup = 3 + 1.4 + 2.2 + 3 + 1 = 10.6 ns

- Z výstupu klopného obvodu na výstup

ClockToQ + NAND2 + NAND4 + NAND6 + StabilniVystup = 3 + 1.4 + 2.2 + 3 + 3 = 12.6 ns

- Ze vstupu na výstup

NestabilniVstup + NAND2 + NAND4 + NAND6 + StabilniVystup = 3 + 1.4 + 2.2 + 3 + 3 = 12.6 ns

- Z výstupu klopného obvodu na vstup klopného obvodu

ClockToQ + NAND2 + NAND4 + NAND6 + Setup = 3 + 1.4 + 2.2 + 3 + 1 = 10.6 ns

Kritická cesta tedy opět trvá 12,6 ns, což znamená maximální frekvenci cca. 79 MHz.

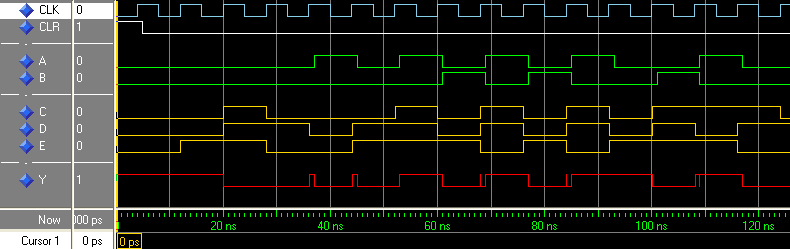

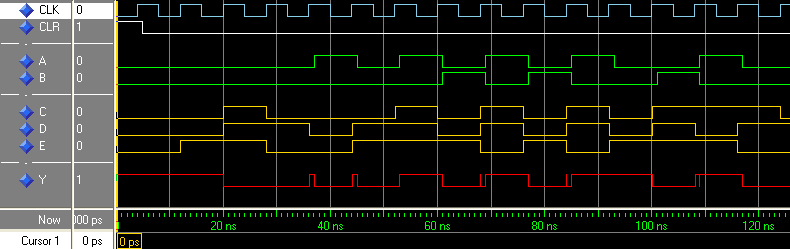

f) Časový diagram získaný ze simulace:

Průchod jsem zvolil stejný jako v případě binárního kódování, tedy:

Q0 =00=> Q13 =00=> Q6 =00=> Q3 =00=> Q0 =01=> Q2 =00=> Q11 =00=> Q4 =01=> Q10 =10=> Q7 =01=> Q1 =10=> Q5 =01=> Q9 =00=> Q11 =10=> Q12 =01=> Q8

Respektive:

Q0 =00=> Q1 =00=> Q6 =00=> Q3 =00=> Q0 =01=> Q2 =00=> Q6 =00=> Q3 =01=> Q0 =10=> Q2 =01=> Q1 =10=> Q5 =01=> Q1 =00=> Q6 =10=> Q12 =01=> Q5

g) Výstup implementace:

Hodnota maximální frekvence je 192,308 MHz, využívá se 7% makrobuněk, 10% Ptermů, 5% registrů, 25% pinů a 4% vstupů funkčních bloků.

Kompletní zpráva o implementaci pro grayův kód je

zde.

5. Závěr

Z výpočtů a z provedených implementací vyplývá, že obě alternativy - binární kódování a grayův kód - jsou srovnatelné jak z hlediska použití

součástek, tak z hlediska časového.